大学生

最后登录1970-1-1

在线时间 小时

注册时间2020-4-22

|

这是驱动的代码

- #include <linux/types.h>

- #include <linux/kernel.h>

- #include <linux/delay.h>

- #include <linux/ide.h>

- #include <linux/init.h>

- #include <linux/module.h>

- #include <linux/errno.h>

- #include <linux/gpio.h>

- #include <linux/cdev.h>

- #include <linux/device.h>

- #include <linux/of.h>

- #include <linux/of_address.h>

- #include <linux/of_gpio.h> //注意这个是新加的

- #include <asm/mach/map.h>

- #include <asm/uaccess.h>

- #include <asm/io.h>

- #define GPIOLED_CNT 1 /* 设备号个数 */

- #define GPIOLED_NAME "gpiorgb" /* 名字 */

- /* gpioled设备结构体 */

- struct gpioled_dev{

- dev_t devid; /* 设备号 */

- struct cdev cdev; /* cdev */

- struct class *class; /* 类 */

- struct device *device; /* 设备 */

- int major; /* 主设备号 */

- int minor; /* 次设备号 */

- struct device_node *nd; /* 设备节点 */

- int rLEd; /* rled使用的GPIO编号*/

- int gLEd; /* gled使用的GPIO编号*/

- int bLEd; /* bled使用的GPIO编号*/

- };

- struct gpioled_dev gpioled; /* led设备 */

- /*

- * @description : 打开设备

- * @param - inode : 传递给驱动的inode

- * @param - filp : 设备文件,file结构体有个叫做private_data的成员变量

- * 一般在open的时候将private_data指向设备结构体。

- * [url=home.php?mod=space&uid=82536]@return[/url] : 0 成功;其他 失败

- */

- static int gpioled_open(struct inode *inode, struct file *filp)

- {

- printk("gpioled open!\n");

- filp->private_data = &gpioled; /* 设置私有数据 */

- return 0;

- }

- /*

- * @description : 从设备读取数据

- * @param - filp : 要打开的设备文件(文件描述符)

- * @param - buf : 返回给用户空间的数据缓冲区

- * @param - cnt : 要读取的数据长度

- * @param - offt : 相对于文件首地址的偏移

- * @return : 读取的字节数,如果为负值,表示读取失败

- */

- static ssize_t gpioled_read(struct file *filp, char __user *buf, size_t cnt, loff_t *offt)

- {

- printk("gpioled read!\n");

- return 0;

- }

- /*

- * @description : 向设备写数据

- * @param - filp : 设备文件,表示打开的文件描述符

- * @param - buf : 要写给设备写入的数据

- * @param - cnt : 要写入的数据长度

- * @param - offt : 相对于文件首地址的偏移

- * @return : 写入的字节数,如果为负值,表示写入失败

- */

- static ssize_t gpioled_write(struct file *filp, const char __user *buf, size_t cnt, loff_t *offt)

- {

- unsigned char write_data; //用于保存接收到的数据

- //读取用户输入

- int error = copy_from_user(&write_data, buf, cnt);

- if(error < 0) {

- return -1;

- }

- /*设置 GPIO1_04 输出电平*/

- if(write_data & 0x04)

- {

- gpio_direction_output(gpioled.rLEd, 0); // GPIO1_04引脚输出低电平,红灯亮

- }

- else

- {

- gpio_direction_output(gpioled.rLEd, 1); // GPIO1_04引脚输出高电平,红灯灭

- }

- /*设置 GPIO4_20 输出电平*/

- if(write_data & 0x02)

- {

- gpio_direction_output(gpioled.gLEd, 0); // GPIO4_20引脚输出低电平,绿灯亮

- }

- else

- {

- gpio_direction_output(gpioled.gLEd, 1); // GPIO4_20引脚输出高电平,绿灯灭

- }

- /*设置 GPIO4_19 输出电平*/

- if(write_data & 0x01)

- {

- gpio_direction_output(gpioled.bLEd, 0); // GPIO4_19引脚输出低电平,蓝灯亮

- }

- else

- {

- gpio_direction_output(gpioled.bLEd, 1); // GPIO4_19引脚输出高电平,蓝灯灭

- }

- return 0;

- }

- /*

- * @description : 关闭/释放设备

- * @param - filp : 要关闭的设备文件(文件描述符)

- * @return : 0 成功;其他 失败

- */

- static int gpioled_release(struct inode *inode, struct file *filp)

- {

- printk("gpioled release!\n");

- return 0;

- }

- /* 设备操作函数 */

- static struct file_operations gpioled_fops = {

- .owner = THIS_MODULE,

- .open = gpioled_open,

- .read = gpioled_read,

- .write = gpioled_write,

- .release = gpioled_release,

- };

- /*

- * @description : LED硬件初始化(IO映射、时钟、GPIO配置)

- * @param : 无

- * @return : 0 成功;其他 失败

- */

- static int gpioled_hardware_init(void)

- {

- int ret;

- /* 获取设备树中的属性数据 */

- /* 1、获取设备节点:rgb_led */

- gpioled.nd = of_find_node_by_path("/rgb_led");

- if(gpioled.nd == NULL)

- {

- printk("gpioled node not find!\r\n");

- return -EINVAL;

- }

- else

- {

- printk("gpioled node find!\r\n");

- }

- /* 2、获取gpio属性, 得到LED编号 */

- gpioled.rLEd = of_get_named_gpio(gpioled.nd, "rgb_led_red", 0);

- gpioled.gLEd = of_get_named_gpio(gpioled.nd, "rgb_led_green", 0);

- gpioled.bLEd = of_get_named_gpio(gpioled.nd, "rgb_led_blue", 0);

- if((gpioled.rLEd < 0) || (gpioled.bLEd < 0) || (gpioled.gLEd < 0))

- {

- printk("can't get LED resources\r\n");

- return -EINVAL;

- }

- else

- {

- printk("redgpio num = %d greengpio num = %d bluegpio num = %d\r\n", gpioled.rLEd,gpioled.gLEd,gpioled.bLEd);

- return -EINVAL;

- }

- ret = gpio_request(gpioled.rLEd,"rgb_led_red");

- ret = gpio_request(gpioled.gLEd,"rgb_led_green");

- ret = gpio_request(gpioled.bLEd,"rgb_led_blue");

- /* 3、设置GPIO为输出, 并默认关闭LED */

- ret = gpio_direction_output(gpioled.rLEd, 1);

- if(ret < 0)

- {

- printk("can't set red LED GPIO direction!\r\n");

- return ret;

- }

-

- ret = gpio_direction_output(gpioled.gLEd, 1);

- if(ret < 0)

- {

- printk("can't set green LED GPIO direction!\r\n");

- return ret;

- }

- ret = gpio_direction_output(gpioled.bLEd, 1);

- if(ret < 0)

- {

- printk("can't set blue LED GPIO direction!\r\n");

- return ret;

- }

- printk("gpio-set Done!\r\n");

-

- return 0;

- }

- /*

- * @description : 驱动出口函数

- * @param : 无

- * @return : 0 成功;其他 失败

- */

- static int __init gpioled_init(void)

- {

- /* 初始化LED */

- int ret = gpioled_hardware_init();

-

- if(ret < 0)

- {

- printk("gpioInit_Faild!\r\n");

- return ret;

- }

- printk("gpio-initDone!\r\n");

- /* 注册字符设备驱动 */

- /* 1、创建设备号 */

- if (gpioled.major) /* 定义了设备号 */

- {

- gpioled.devid = MKDEV(gpioled.major, 0);

- register_chrdev_region(gpioled.devid, GPIOLED_CNT, GPIOLED_NAME);

- }

- else /* 没有定义设备号 */

- {

- alloc_chrdev_region(&gpioled.devid, 0, GPIOLED_CNT, GPIOLED_NAME); /* 申请设备号 */

- gpioled.major = MAJOR(gpioled.devid); /* 获取分配号的主设备号 */

- gpioled.minor = MINOR(gpioled.devid); /* 获取分配号的次设备号 */

- }

- printk("device number get!\r\n");

- printk("gpioled major=%d,minor=%d\n",gpioled.major, gpioled.minor);

-

- /* 2、初始化cdev */

- gpioled.cdev.owner = THIS_MODULE;

- cdev_init(&gpioled.cdev, &gpioled_fops);

- printk("cdev-initDone!\r\n");

- /* 3、添加一个cdev */

- cdev_add(&gpioled.cdev, gpioled.devid, GPIOLED_CNT);

- /* 4、创建类 */

- gpioled.class = class_create(THIS_MODULE, GPIOLED_NAME);

- if (IS_ERR(gpioled.class))

- {

- return PTR_ERR(gpioled.class);

- }

- printk("device_class-initDone!\r\n");

- /* 5、创建设备 */

- gpioled.device = device_create(gpioled.class, NULL, gpioled.devid, NULL, GPIOLED_NAME);

- if (IS_ERR(gpioled.device))

- {

- return PTR_ERR(gpioled.device);

- }

- printk("createDevice-initDone!\r\n");

- printk("gpioled init done!\n");

- return 0;

- }

- /*

- * @description : 驱动出口函数

- * @param : 无

- * @return : 无

- */

- static void __exit gpioled_exit(void)

- {

- /* 注销字符设备驱动 */

- cdev_del(&gpioled.cdev);/* 删除cdev */

- unregister_chrdev_region(gpioled.devid, GPIOLED_CNT); /* 注销设备号 */

- device_destroy(gpioled.class, gpioled.devid);

- class_destroy(gpioled.class);

-

- printk("gpioled exit done!\n");

- }

- /*

- * 将上面两个函数指定为驱动的入口和出口函数

- */

- module_init(gpioled_init);

- module_exit(gpioled_exit);

- /*

- * LICENSE和作者信息

- */

- MODULE_LICENSE("GPL");

- MODULE_AUTHOR("zzlyang");

这是我的设备树文件

- /*

- * Copyright (C) 2016 Freescale Semiconductor, Inc.

- *

- * This program is free software; you can redistribute it and/or modify

- * it under the terms of the GNU General Public License version 2 as

- * published by the Free Software Foundation.

- */

- /dts-v1/;

- #include <dt-bindings/input/input.h>

- #include "imx6ull.dtsi"

- / {

- model = "Freescale i.MX6 ULL 14x14 EVK Board";

- compatible = "fsl,imx6ull-14x14-evk", "fsl,imx6ull";

- chosen {

- stdout-path = &uart1;

- };

- memory {

- reg = <0x80000000 0x20000000>;

- };

- reserved-memory {

- #address-cells = <1>;

- #size-cells = <1>;

- ranges;

- linux,cma {

- compatible = "shared-dma-pool";

- reusable;

- size = <0x14000000>;

- linux,cma-default;

- };

- };

- backlight {

- compatible = "pwm-backlight";

- pwms = <&pwm1 0 1000000>;

- brightness-levels = <0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100>;

- default-brightness-level = <90>;

- status = "okay";

- };

- pxp_v4l2 {

- compatible = "fsl,imx6ul-pxp-v4l2", "fsl,imx6sx-pxp-v4l2", "fsl,imx6sl-pxp-v4l2";

- status = "okay";

- };

- regulators {

- compatible = "simple-bus";

- #address-cells = <1>;

- #size-cells = <0>;

- reg_can_3v3: regulator@0 {

- compatible = "regulator-fixed";

- reg = <0>;

- regulator-name = "can-3v3";

- regulator-min-microvolt = <3300000>;

- regulator-max-microvolt = <3300000>;

- /*gpios = <&gpio_spi 3 GPIO_ACTIVE_LOW>;*/

- };

- reg_wifi_vmmc: regulator@1 {

- compatible = "regulator-fixed";

- regulator-name = "WIFI_3V3";

- regulator-min-microvolt = <3300000>;

- regulator-max-microvolt = <3300000>;

- gpio = <&gpio1 1 GPIO_ACTIVE_HIGH>;

- enable-active-high;

- };

- reg_vref_3v3: regulator@2 {

- compatible = "regulator-fixed";

- regulator-name = "vref-3v3";

- regulator-min-microvolt = <3300000>;

- regulator-max-microvolt = <3300000>;

- };

- /*

- reg_gpio_dvfs: regulator-gpio {

- compatible = "regulator-gpio";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_dvfs>;

- regulator-min-microvolt = <1300000>;

- regulator-max-microvolt = <1400000>;

- regulator-name = "gpio_dvfs";

- regulator-type = "voltage";

- gpios = <&gpio5 3 GPIO_ACTIVE_HIGH>;

- states = <1300000 0x1 1400000 0x0>;

- };

- reg_bt: regulator-bt-reg {

- compatible = "regulator-gpio";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_dvfs>;

- regulator-min-microvolt = <1300000>;

- regulator-max-microvolt = <1400000>;

- regulator-name = "gpio_dvfs";

- regulator-type = "voltage";

- gpios = <&gpio5 3 GPIO_ACTIVE_HIGH>;

- states = <1300000 0x1 1400000 0x0>;

- };*/

- };

- /*

- leds {

- compatible = "gpio-leds";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_led>;

- led0: cpu {

- label = "cpu";

- // gpios = <&gpio5 3 GPIO_ACTIVE_HIGH>;

- default-state = "off";

- linux,default-trigger = "heartbeat";

- };

- };

- */

- /*

- pwm_leds{

- compatible = "pwm-leds";

- status = "okay";

- red {

- label = "red";

- active-low;

- pwms = <&pwm3 0 5000>;

- max-brightness = <255>;

- };

- blue {

- label = "blue";

- active-low;

- pwms = <&pwm7 0 5000>;

- max-brightness = <255>;

- };

- green {

- label = "green";

- active-low;

- pwms = <&pwm8 0 5000>;

- max-brightness = <255>;

- };

- };

- */

- ir_recv:ir-receiver {

- compatible = "gpio-ir-receiver";

- #gpio-cells = <1>;

- gpios = <&gpio1 21 GPIO_ACTIVE_LOW>;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_remote_control>;

- linux,rc-map-name = "rc-lirc";

- status = "okay";

- };

- /*

- gpio-keys {

- compatible = "gpio-keys";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_gpio_keys>;

- Key0{

- label = "Key 0";

- gpios = <&gpio5 1 GPIO_ACTIVE_HIGH>;

- linux,code = <KEY_0>;

- };

- };

- */

- sound {

- compatible = "fsl,imx6ul-evk-wm8960",

- "fsl,imx-audio-wm8960";

- model = "wm8960-audio";

- cpu-dai = <&sai2>;

- audio-codec = <&codec>;

- asrc-controller = <&asrc>;

- codec-master;

- gpr = <&gpr 4 0x100000 0x100000>;

- /*

- * hp-det = <hp-det-pin hp-det-polarity>;

- * hp-det-pin: JD1 JD2 or JD3

- * hp-det-polarity = 0: hp detect high for headphone

- * hp-det-polarity = 1: hp detect high for speaker

- */

- hp-det = <3 1>;

- /*hp-det-gpios = <&gpio5 4 0>;

- mic-det-gpios = <&gpio5 4 0>;*/

- audio-routing =

- "Headphone Jack", "HP_L",

- "Headphone Jack", "HP_R",

- "Ext Spk", "SPK_LP",

- "Ext Spk", "SPK_LN",

- "Ext Spk", "SPK_RP",

- "Ext Spk", "SPK_RN",

- "LINPUT2", "Mic Jack",

- "LINPUT3", "Mic Jack",

- "RINPUT1", "Main MIC",

- "RINPUT2", "Main MIC",

- "Mic Jack", "MICB",

- "Main MIC", "MICB",

- "CPU-Playback", "ASRC-Playback",

- "Playback", "CPU-Playback",

- "ASRC-Capture", "CPU-Capture",

- "CPU-Capture", "Capture";

- status = "okay";

- };

- spi4 {

- compatible = "spi-gpio";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_spi4>;

- pinctrl-assert-gpios = <&gpio5 8 GPIO_ACTIVE_LOW>;

- status = "okay";

- gpio-sck = <&gpio5 11 0>;

- gpio-mosi = <&gpio5 10 0>;

- cs-gpios = <&gpio5 7 0>;

- num-chipselects = <1>;

- #address-cells = <1>;

- #size-cells = <0>;

- gpio_spi: gpio_spi@0 {

- compatible = "fairchild,74hc595";

- gpio-controller;

- #gpio-cells = <2>;

- reg = <0>;

- registers-number = <1>;

- registers-default = /bits/ 8 <0x57>;

- spi-max-frequency = <100000>;

- };

- };

- sound-spdif {

- compatible = "fsl,imx-audio-spdif";

- model = "imx-spdif";

- spdif-controller = <&spdif>;

- spdif-in;

- spdif-out;

- };

- sii902x_reset: sii902x-reset {

- compatible = "gpio-reset";

- reset-gpios = <&gpio_spi 0 GPIO_ACTIVE_LOW>;

- reset-delay-us = <100000>;

- #reset-cells = <0>;

- };

- ds18b20{

- compatible = "w1-gpio";

- gpios = <&gpio1 2 GPIO_ACTIVE_HIGH>;

- linux,open-drain;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_onewire>;

- status = "disable";

- };

- dht11{

- compatible = "dht11";

- gpios = <&gpio1 2 GPIO_ACTIVE_LOW>;

- linux,open-drain;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_onewire>;

- status = "okay";

- };

-

- oled {

- compatible = "sh1106";

- #address-cells = <1>;

- #size-cells = <0>;

- reg = <0x4001b8b0 0x00000004>;

- status = "okay";

-

- };

- beep {

- #address-cells = <1>;

- #size-cells = <1>;

- compatible="beep";

- status = "okay";

- reg=<0x20c406C 0x04

- 0x20E0000 0X04

- 0X20E031C 0X04

- 0X209C000 0X04

- 0X209C004 0X04 >;

- };

-

-

- gpioled{

- compatible = "gpioled";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_gpioled>;

- led-gpio = <&gpio5 3 GPIO_ACTIVE_LOW>; //低电平有效

- status = "okay";

- };

-

-

- myled{

- #address-cells = <1>;

- #size-cells = <1>;

- compatible = "myboard-led";

- status = "okay";

- reg = < 0X020C406C 0x04 /*CCM_CCGR1_BASE*/

- 0X02290014 0x04 /*SW_MUX_SNVS_TAMPER3_BASE*/

- 0X02290058 0x04 /*SW_PAD_SNVS_TAMPER3_BASE*/

- 0X020AC000 0x04 /*GPIO5_DR_BASE*/

- 0X020AC004 0x04 >; /*GPIO5_GDIR_BASE*/

- };

-

- gpiobeep{

- compatible = "gpiobeep";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_beep>;

- beep-gpios = <&gpio1 19 GPIO_ACTIVE_HIGH>;

- status = "okay";

- };

-

- swkey {

- #address-cells = <1>;

- #size-cells = <1>;

- compatible = "myboard-key";

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_key>;

- key1-gpio = <&gpio5 1 GPIO_ACTIVE_HIGH>; /* SW2 */

- key2-gpio = <&gpio5 11 GPIO_ACTIVE_LOW>; /* SW4 */

- status = "okay";

- };

-

- rgb_led{

- #address-cells = <1>;

- #size-cells = <1>;

- pinctrl-name = "default";

- compatible = "rgb-led";

- pinctrl-0 = <&pinctrl_rgb_led>;

- rgb_led_red = <&gpio1 4 GPIO_ACTIVE_LOW>;

- rgb_led_green = <&gpio4 20 GPIO_ACTIVE_LOW>;

- rgb_led_blue = <&gpio4 19 GPIO_ACTIVE_LOW>;

- status = "okay";

- };

- };

- &cpu0 {

- arm-supply = <®_arm>;

- soc-supply = <®_soc>;

- clock-frequency = <800000000>;

- /*dc-supply = <®_gpio_dvfs>;*/

- };

- &clks {

- assigned-clocks = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

- assigned-clock-rates = <786432000>;

- };

- &fec1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_enet1>;

- phy-mode = "rmii";

- phy-handle = <ðphy0>;

- status = "okay";

- };

- &fec2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_enet2>;

- phy-mode = "rmii";

- phy-handle = <ðphy1>;

- status = "okay";

- mdio {

- #address-cells = <1>;

- #size-cells = <0>;

- ethphy0: ethernet-phy@2 {

- compatible = "ethernet-phy-ieee802.3-c22";

- reg = <2>;

- };

- ethphy1: ethernet-phy@1 {

- compatible = "ethernet-phy-ieee802.3-c22";

- reg = <1>;

- };

- };

- };

- &flexcan1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_flexcan1>;

- /*xceiver-supply = <®_can_3v3>;*/

- status = "okay";

- };

- /*

- &flexcan2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_flexcan2>;

- /*xceiver-supply = <®_can_3v3>;

- status = "okay"; /*can & UART2 can not use as same time

- };*/

- &gpc {

- fsl,cpu_pupscr_sw2iso = <0x1>;

- fsl,cpu_pupscr_sw = <0x0>;

- fsl,cpu_pdnscr_iso2sw = <0x1>;

- fsl,cpu_pdnscr_iso = <0x1>;

- fsl,ldo-bypass = <0>; /* DCDC, ldo-enable */

- };

- &i2c1 {

- clock-frequency = <100000>;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_i2c1>;

- status = "okay";

- mpu6050@68 {

- compatible = "mpu6050,INV_MPU6050";

- reg = <0x68>;

- position = <1>;

- };

- gt9xx@5d {

- compatible = "goodix,gt9xx";

- reg = <0x5d>;

- status = "okay";

- interrupt-parent = <&gpio5>;

- interrupts = <9 IRQ_TYPE_EDGE_FALLING>;

- pinctrl-names = "pinctrl_tsc_reset","pinctrl_tsc_irq";

- pinctrl-0 = <&pinctrl_tsc_reset>;

- pinctrl-1 = <&pinctrl_tsc_irq>;

- /*pinctrl-names = "default", "int-output-low", "int-output-high", "int-input";

- pinctrl-0 = <&ts_int_default>;

- pinctrl-1 = <&ts_int_output_low>;

- pinctrl-2 = <&ts_int_output_high>;

- pinctrl-3 = <&ts_int_input>;

- */

- reset-gpios = <&gpio3 4 GPIO_ACTIVE_LOW>;

- irq-gpios = <&gpio5 9 IRQ_TYPE_EDGE_FALLING>;

- irq-flags = <2>; /*1:rising 2: falling*/

- touchscreen-max-id = <1>;

- touchscreen-size-x = <800>;

- touchscreen-size-y = <480>;

- touchscreen-max-w = <1024>;

- touchscreen-max-p = <1024>;

- /*touchscreen-key-map = <172>, <158>;*/ /*KEY_HOMEPAGE, KEY_BACK*/

- goodix,type-a-report = <0>;

- goodix,driver-send-cfg = <0>;

- goodix,create-wr-node = <1>;

- goodix,wakeup-with-reset = <0>;

- goodix,resume-in-workqueue = <0>;

- goodix,int-sync = <1>;

- goodix,swap-x2y = <0>;

- goodix,esd-protect = <0>;

- goodix,pen-suppress-finger = <0>;

- goodix,auto-update = <0>;

- goodix,auto-update-cfg = <0>;

- goodix,power-off-sleep = <0>;

- /*7*/

- goodix,cfg-group0 = [

- 00 20 03 E0 01 05 0D 00 01 08

- 28 0F 50 32 03 05 00 00 00 00

- 00 00 00 00 00 00 00 8A 2A 0C

- 45 47 0C 08 00 00 00 02 02 2D

- 00 00 00 00 00 03 64 32 00 00

- 00 28 64 94 C5 02 07 00 00 04

- 9C 2C 00 8F 34 00 84 3F 00 7C

- 4C 00 77 5B 00 77 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 18 16 14 12 10 0E 0C 0A

- 08 06 04 02 FF FF 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 16 18 1C 1D 1E 1F 20 21

- 22 24 13 12 10 0F 0A 08 06 04

- 02 00 FF FF FF FF FF FF 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 24 01

- ];

- /*4.3*/

- goodix,cfg-group1 = [

- 97 E0 01 10 01 05 0D 00 01 00

- 00 05 5A 46 53 11 00 00 11 11

- 14 14 14 22 0A 04 00 00 00 00

- 00 00 53 00 14 00 00 84 00 00

- 3C 00 00 64 1E 28 87 27 08 32

- 34 05 0D 20 33 60 11 02 24 00

- 00 64 80 80 14 02 00 00 54 89

- 68 85 6D 82 72 80 76 7D 7B 7B

- 00 00 00 00 00 00 00 F0 50 3C

- FF FF 07 00 00 00 02 14 14 03

- 04 00 21 64 0A 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 32 20 50 3C 3C 00 00 00 00 00

- 0D 06 0C 05 0B 04 0A 03 FF FF

- FF FF FF FF 00 01 02 03 04 05

- 06 07 08 09 0A 0B 0C 0D FF FF

- FF FF FF FF FF FF FF FF FF FF

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 3C 00 05 1E 00 02

- 2A 1E 19 14 02 00 03 0A 05 00

- 00 00 00 00 00 00 01 FF FF 86

- 22 03 00 00 33 00 0F 00 00 00

- 50 3C 50 00 00 00 00 2A 01

- ];

- /*5*/

- goodix,cfg-group2 = [

- 00 20 03 E0 01 05 3C 00 01 08

- 28 0C 50 32 03 05 00 00 00 00

- 00 00 00 17 19 1E 14 8B 2B 0D

- 33 35 0C 08 00 00 00 9A 03 11

- 00 01 00 00 00 00 00 32 00 00

- 00 20 58 94 C5 02 00 00 00 04

- B0 23 00 93 2B 00 7B 35 00 69

- 41 00 5B 4F 00 5B 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 02 04 06 08 0A 0C 0E 10

- 12 14 16 18 1A FF 00 00 00 00

- 00 00 00 00 00 00 00 00 00 00

- 00 00 00 02 04 06 08 0A 0C 0F

- 10 12 13 16 18 1C 1D 1E 1F 20

- 21 22 24 26 FF FF FF FF 00 00

- 00 FF FF FF FF FF FF FF FF FF

- FF FF FF FF 48 01

- ];

- };

- /*

- mag3110@0e {

- compatible = "fsl,mag3110";

- reg = <0x0e>;

- position = <2>;

- };

- fxls8471@1e {

- compatible = "fsl,fxls8471";

- reg = <0x1e>;

- position = <0>;

- interrupt-parent = <&gpio5>;

- interrupts = <0 8>;

- };*/

- };

- &i2c2 {

- clock_frequency = <100000>;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_i2c2>;

- status = "okay";

- codec: wm8960@1a {

- compatible = "wlf,wm8960";

- reg = <0x1a>;

- clocks = <&clks IMX6UL_CLK_SAI2>;

- clock-names = "mclk";

- wlf,shared-lrclk;

- };

- sii902x: sii902x@39 {

- compatible = "SiI,sii902x";

- pinctrl-names = "default";

- reset-names="sii902x";

- pinctrl-0 = <&pinctrl_sii902x>;

- resets = <&sii902x_reset>;

- interrupt-parent = <&gpio1>;

- interrupts = <18 IRQ_TYPE_EDGE_FALLING>;

- mode_str ="1280x720M@60";

- bits-per-pixel = <16>;

- reg = <0x39>;

- status = "okay"; /* HDMI 使能 */

- };

- ov5640: ov5640@3c {

- compatible = "ovti,ov5640";

- reg = <0x3c>;

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_csi1>;

- clocks = <&clks IMX6UL_CLK_CSI>;

- clock-names = "csi_mclk";

- pwn-gpios = <&gpio_spi 6 1>;

- rst-gpios = <&gpio_spi 5 0>;

- csi_id = <0>;

- mclk = <24000000>;

- mclk_source = <0>;

- status = "disable"; /* 摄像头使能 */

- port {

- ov5640_ep: endpoint {

- remote-endpoint = <&csi1_ep>;

- };

- };

- };

- };

- &csi {

- status = "disable"; /* 摄像头总线使能 */

- port {

- csi1_ep: endpoint {

- remote-endpoint = <&ov5640_ep>;

- };

- };

- };

- &iomuxc {

- pinctrl-names = "default";

- imx6ul-evk {

- pinctrl_gpmi_nand: gpmi-nand {

- fsl,pins = <

- MX6UL_PAD_NAND_CLE__RAWNAND_CLE 0xb0b1

- MX6UL_PAD_NAND_ALE__RAWNAND_ALE 0xb0b1

- MX6UL_PAD_NAND_WP_B__RAWNAND_WP_B 0xb0b1

- MX6UL_PAD_NAND_READY_B__RAWNAND_READY_B 0xb000

- MX6UL_PAD_NAND_CE0_B__RAWNAND_CE0_B 0xb0b1

- MX6UL_PAD_NAND_CE1_B__RAWNAND_CE1_B 0xb0b1

- MX6UL_PAD_NAND_RE_B__RAWNAND_RE_B 0xb0b1

- MX6UL_PAD_NAND_WE_B__RAWNAND_WE_B 0xb0b1

- MX6UL_PAD_NAND_DATA00__RAWNAND_DATA00 0xb0b1

- MX6UL_PAD_NAND_DATA01__RAWNAND_DATA01 0xb0b1

- MX6UL_PAD_NAND_DATA02__RAWNAND_DATA02 0xb0b1

- MX6UL_PAD_NAND_DATA03__RAWNAND_DATA03 0xb0b1

- MX6UL_PAD_NAND_DATA04__RAWNAND_DATA04 0xb0b1

- MX6UL_PAD_NAND_DATA05__RAWNAND_DATA05 0xb0b1

- MX6UL_PAD_NAND_DATA06__RAWNAND_DATA06 0xb0b1

- MX6UL_PAD_NAND_DATA07__RAWNAND_DATA07 0xb0b1

- >;

- };

- pinctrl_remote_control: remote_control {

- fsl,pins = <

- MX6UL_PAD_UART2_RX_DATA__GPIO1_IO21 0x000010B1 /* remote control add by pengjie 20190703*/

- >;

- };

- pinctrl_csi1: csi1grp {

- fsl,pins = <

- MX6UL_PAD_CSI_MCLK__CSI_MCLK 0x1b088

- MX6UL_PAD_CSI_PIXCLK__CSI_PIXCLK 0x1b088

- MX6UL_PAD_CSI_VSYNC__CSI_VSYNC 0x1b088

- MX6UL_PAD_CSI_HSYNC__CSI_HSYNC 0x1b088

- MX6UL_PAD_CSI_DATA00__CSI_DATA02 0x1b088

- MX6UL_PAD_CSI_DATA01__CSI_DATA03 0x1b088

- MX6UL_PAD_CSI_DATA02__CSI_DATA04 0x1b088

- MX6UL_PAD_CSI_DATA03__CSI_DATA05 0x1b088

- MX6UL_PAD_CSI_DATA04__CSI_DATA06 0x1b088

- MX6UL_PAD_CSI_DATA05__CSI_DATA07 0x1b088

- MX6UL_PAD_CSI_DATA06__CSI_DATA08 0x1b088

- MX6UL_PAD_CSI_DATA07__CSI_DATA09 0x1b088

- >;

- };

- pinctrl_enet1: enet1grp {

- fsl,pins = <

- MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

- MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

- MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

- MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

- MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

- MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

- MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

- MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001b031

- >;

- };

- pinctrl_enet2: enet2grp {

- fsl,pins = <

- MX6UL_PAD_GPIO1_IO07__ENET2_MDC 0x1b0b0

- MX6UL_PAD_GPIO1_IO06__ENET2_MDIO 0x1b0b0

- MX6UL_PAD_ENET2_RX_EN__ENET2_RX_EN 0x1b0b0

- MX6UL_PAD_ENET2_RX_ER__ENET2_RX_ER 0x1b0b0

- MX6UL_PAD_ENET2_RX_DATA0__ENET2_RDATA00 0x1b0b0

- MX6UL_PAD_ENET2_RX_DATA1__ENET2_RDATA01 0x1b0b0

- MX6UL_PAD_ENET2_TX_EN__ENET2_TX_EN 0x1b0b0

- MX6UL_PAD_ENET2_TX_DATA0__ENET2_TDATA00 0x1b0b0

- MX6UL_PAD_ENET2_TX_DATA1__ENET2_TDATA01 0x1b0b0

- MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001b031

- >;

- };

- pinctrl_flexcan1: flexcan1grp{

- fsl,pins = <

- MX6UL_PAD_UART3_RTS_B__FLEXCAN1_RX 0x1b020

- MX6UL_PAD_UART3_CTS_B__FLEXCAN1_TX 0x1b020

- >;

- };

- pinctrl_flexcan2: flexcan2grp{

- fsl,pins = <

- MX6UL_PAD_UART2_RTS_B__FLEXCAN2_RX 0x1b020

- MX6UL_PAD_UART2_CTS_B__FLEXCAN2_TX 0x1b020

- >;

- };

- pinctrl_i2c1: i2c1grp {

- fsl,pins = <

- MX6UL_PAD_UART4_TX_DATA__I2C1_SCL 0x4001b8b0

- MX6UL_PAD_UART4_RX_DATA__I2C1_SDA 0x4001b8b0

- >;

- };

- pinctrl_i2c2: i2c2grp {

- fsl,pins = <

- MX6UL_PAD_UART5_TX_DATA__I2C2_SCL 0x4001b8b0

- MX6UL_PAD_UART5_RX_DATA__I2C2_SDA 0x4001b8b0

- >;

- };

- pinctrl_lcdif_dat: lcdifdatgrp {

- fsl,pins = <

- MX6UL_PAD_LCD_DATA00__LCDIF_DATA00 0x79

- MX6UL_PAD_LCD_DATA01__LCDIF_DATA01 0x79

- MX6UL_PAD_LCD_DATA02__LCDIF_DATA02 0x79

- MX6UL_PAD_LCD_DATA03__LCDIF_DATA03 0x79

- MX6UL_PAD_LCD_DATA04__LCDIF_DATA04 0x79

- MX6UL_PAD_LCD_DATA05__LCDIF_DATA05 0x79

- MX6UL_PAD_LCD_DATA06__LCDIF_DATA06 0x79

- MX6UL_PAD_LCD_DATA07__LCDIF_DATA07 0x79

- MX6UL_PAD_LCD_DATA08__LCDIF_DATA08 0x79

- MX6UL_PAD_LCD_DATA09__LCDIF_DATA09 0x79

- MX6UL_PAD_LCD_DATA10__LCDIF_DATA10 0x79

- MX6UL_PAD_LCD_DATA11__LCDIF_DATA11 0x79

- MX6UL_PAD_LCD_DATA12__LCDIF_DATA12 0x79

- MX6UL_PAD_LCD_DATA13__LCDIF_DATA13 0x79

- MX6UL_PAD_LCD_DATA14__LCDIF_DATA14 0x79

- MX6UL_PAD_LCD_DATA15__LCDIF_DATA15 0x79

- MX6UL_PAD_LCD_DATA16__LCDIF_DATA16 0x79

- MX6UL_PAD_LCD_DATA17__LCDIF_DATA17 0x79

- MX6UL_PAD_LCD_DATA18__LCDIF_DATA18 0x79

- MX6UL_PAD_LCD_DATA19__LCDIF_DATA19 0x79

- MX6UL_PAD_LCD_DATA20__LCDIF_DATA20 0x79

- MX6UL_PAD_LCD_DATA21__LCDIF_DATA21 0x79

- MX6UL_PAD_LCD_DATA22__LCDIF_DATA22 0x79

- MX6UL_PAD_LCD_DATA23__LCDIF_DATA23 0x79

- >;

- };

- pinctrl_lcdif_ctrl: lcdifctrlgrp {

- fsl,pins = <

- MX6UL_PAD_LCD_CLK__LCDIF_CLK 0x79

- MX6UL_PAD_LCD_ENABLE__LCDIF_ENABLE 0x79

- MX6UL_PAD_LCD_HSYNC__LCDIF_HSYNC 0x79

- MX6UL_PAD_LCD_VSYNC__LCDIF_VSYNC 0x79

- >;

- };

- pinctrl_pwm1: pwm1grp {

- fsl,pins = <

- MX6UL_PAD_GPIO1_IO08__PWM1_OUT 0x000010B1

- >;

- };

- pinctrl_pwm3: pwm3grp {

- fsl,pins = <

- MX6UL_PAD_GPIO1_IO04__PWM3_OUT 0x000010B1

- >;

- };

- pinctrl_pwm7: pwm7grp {

- fsl,pins = <

- MX6UL_PAD_CSI_VSYNC__PWM7_OUT 0x000010B1

- >;

- };

- pinctrl_pwm8: pwm8grp {

- fsl,pins = <

- MX6UL_PAD_CSI_HSYNC__PWM8_OUT 0x000010B1

- >;

- };

- pinctrl_qspi: qspigrp {

- fsl,pins = <

- MX6UL_PAD_NAND_WP_B__QSPI_A_SCLK 0x70a1

- MX6UL_PAD_NAND_READY_B__QSPI_A_DATA00 0x70a1

- MX6UL_PAD_NAND_CE0_B__QSPI_A_DATA01 0x70a1

- MX6UL_PAD_NAND_CE1_B__QSPI_A_DATA02 0x70a1

- MX6UL_PAD_NAND_CLE__QSPI_A_DATA03 0x70a1

- MX6UL_PAD_NAND_DQS__QSPI_A_SS0_B 0x70a1

- >;

- };

- pinctrl_sai2: sai2grp {

- fsl,pins = <

- MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

- MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

- MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

- MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

- MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

- >;

- };

- pinctrl_spdif: spdifgrp {

- fsl,pins = <

- MX6UL_PAD_JTAG_MOD__SPDIF_OUT 0x1b0b0

- MX6UL_PAD_GPIO1_IO09__SPDIF_IN 0x1b0b0

- >;

- };

- pinctrl_uart1: uart1grp {

- fsl,pins = <

- MX6UL_PAD_UART1_TX_DATA__UART1_DCE_TX 0x1b0b1

- MX6UL_PAD_UART1_RX_DATA__UART1_DCE_RX 0x1b0b1

- >;

- };

- pinctrl_uart2: uart2grp {

- fsl,pins = <

- MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

- MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

- >;

- };

- pinctrl_uart3: uart3grp {

- fsl,pins = <

- MX6UL_PAD_UART3_TX_DATA__UART3_DCE_TX 0x1b0b1

- MX6UL_PAD_UART3_RX_DATA__UART3_DCE_RX 0x1b0b1

- >;

- };

- pinctrl_uart2dte: uart2dtegrp {

- fsl,pins = <

- MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

- MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

- /*MX6UL_PAD_UART3_RX_DATA__UART2_DCE_RTS 0x1b0b1

- MX6UL_PAD_UART3_TX_DATA__UART2_DCE_CTS 0x1b0b1 pengjie 20190622*/

- MX6UL_PAD_UART2_CTS_B__UART2_DCE_CTS 0x1b0b1

- MX6UL_PAD_UART2_RTS_B__UART2_DCE_RTS 0x1b0b1

- >;

- };

- pinctrl_485: 485grp {

- fsl,pins = <

- MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

- MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

- MX6UL_PAD_UART2_CTS_B__UART2_DCE_CTS 0x1b0b1 /* RS485 RE/DE */

- >;

- };

- pinctrl_usdhc1: usdhc1grp {

- fsl,pins = <

- MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x17059

- MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x10071

- MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x17059

- MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x17059

- MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x17059

- MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x17059

- >;

- };

- pinctrl_usdhc1_100mhz: usdhc1grp100mhz {

- fsl,pins = <

- MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170b9

- MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100b9

- MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170b9

- MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170b9

- MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170b9

- MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170b9

- >;

- };

- pinctrl_usdhc1_200mhz: usdhc1grp200mhz {

- fsl,pins = <

- MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170f9

- MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100f9

- MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170f9

- MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170f9

- MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170f9

- MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170f9

- >;

- };

- pinctrl_usdhc2: usdhc2grp {

- fsl,pins = <

- MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069

- MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

- MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

- MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

- MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

- MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

- >;

- };

- pinctrl_usdhc2_8bit: usdhc2grp_8bit {

- fsl,pins = <

- MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069

- MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

- MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

- MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

- MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

- MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

- MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x17059

- MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x17059

- MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x17059

- MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x17059

- >;

- };

- pinctrl_usdhc2_8bit_100mhz: usdhc2grp_8bit_100mhz {

- fsl,pins = <

- MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9

- MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9

- MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9

- MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9

- MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9

- MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9

- MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170b9

- MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170b9

- MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170b9

- MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170b9

- >;

- };

- pinctrl_usdhc2_8bit_200mhz: usdhc2grp_8bit_200mhz {

- fsl,pins = <

- MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9

- MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9

- MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9

- MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9

- MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9

- MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9

- MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170f9

- MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170f9

- MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170f9

- MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170f9

- >;

- };

- pinctrl_tsc_reset: tscresetgrp {

- fsl,pins = <

- /* used for tsc reset */

- MX6UL_PAD_LCD_RESET__GPIO3_IO04 0x05

- >;

- };

- pinctrl_onewire: onewire {

- fsl,pins = <

- //MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0x000090B1 DHT11

- MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0x400138B1

- >;

- };

- pinctrl_sii902x: hdmigrp {

- fsl,pins = <

- MX6UL_PAD_UART1_CTS_B__GPIO1_IO18 0x59

- >;

- };

-

- pinctrl_gpioled: gpioledgrp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER3__GPIO5_IO03 0x010b0

- >;

- };

-

- pinctrl_adc1: adc1grp{

- fsl,pins = <

- MX6UL_PAD_GPIO1_IO03__GPIO1_IO03 0x000010B1

- >;

- };

-

- pinctrl_key: keygrp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER1__GPIO5_IO01 0x3080 /* SW2 */

- MX6ULL_PAD_BOOT_MODE1__GPIO5_IO11 0xF080 /* SW4 */

- >;

- };

-

- pinctrl_beep: beepgrp{

- fsl,pins = <

- MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x000050B1

- >;

- };

-

- pinctrl_rgb_led:rgb_led{

- fsl,pins = <

- MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0x000050B1

- MX6UL_PAD_CSI_HSYNC__GPIO4_IO20 0x000050B1

- MX6UL_PAD_CSI_VSYNC__GPIO4_IO19 0x000050B1

- >;

- };

- };

- };

- &iomuxc_snvs {

- pinctrl-names = "default_snvs";

- pinctrl-0 = <&pinctrl_tsc_irq>;

- imx6ul-evk {

- /* MPU6050 intterrupt*/

- pinctrl_hog_2: hoggrp-2 {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER0__GPIO5_IO00 0x80000000

- >;

- };

- /*

- pinctrl_dvfs: dvfsgrp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER3__GPIO5_IO03 0x79

- >;

- };

- */

- pinctrl_led: ledgrp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER3__GPIO5_IO03 0x1b0b0

- >;

- };

- /*

- pinctrl_leds: ledsgrp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER3__GPIO5_IO03 0x010b0

- >;

- };

- */

-

- pinctrl_spi4: spi4grp {

- fsl,pins = <

- MX6ULL_PAD_BOOT_MODE0__GPIO5_IO10 0x70a1

- MX6ULL_PAD_BOOT_MODE1__GPIO5_IO11 0x70a1

- MX6ULL_PAD_SNVS_TAMPER7__GPIO5_IO07 0x70a1

- MX6ULL_PAD_SNVS_TAMPER8__GPIO5_IO08 0x80000000

- >;

- };

-

- pinctrl_sai2_hp_det_b: sai2_hp_det_grp {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER4__GPIO5_IO04 0x000110A1

- >;

- };

- pinctrl_tsc_irq: tsc_irq {

- fsl,pins = <

- MX6ULL_PAD_SNVS_TAMPER9__GPIO5_IO09 0x4001b8b0

- >;

- };

- };

- };

- &lcdif {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_lcdif_dat

- &pinctrl_lcdif_ctrl>;

- display = <&display0>;

- status = "okay";

- display0: display@0 {

- bits-per-pixel = <16>;

- bus-width = <24>;

- display-timings {

- native-mode = <&timing0>;

- /*

- timing0: timing0 {

- mode_name = "hdmi";

- clock-frequency = <27000000>;

- mode_name = "hdmi";

- clock-frequency = <27000000>;

- hactive = <1360>;

- vactive = <768>;

- hfront-porch = <8>;

- hback-porch = <4>;

- hsync-len = <41>;

- vback-porch = <4>;

- vfront-porch = <2>;

- vsync-len = <10>;

- hsync-active = <0>;

- vsync-active = <0>;

- de-active = <1>;

- pixelclk-active = <0>;

- };

- timing0: timing0 {

- mode_name = "TFT43AB";

- clock-frequency = <9000000>;

- hactive = <480>;

- vactive = <272>;

- hfront-porch = <8>;

- hback-porch = <2>;

- hsync-len = <41>;

- vback-porch = <4>;

- vfront-porch = <4>;

- vsync-len = <10>;

- hsync-active = <0>;

- vsync-active = <0>;

- de-active = <1>;

- pixelclk-active = <0>;

- };

- */

- timing0: timing0 {

- mode_name = "TFT50AB";

- clock-frequency = <27000000>;

- hactive = <800>;

- vactive = <480>;

- hfront-porch = <23>;

- hback-porch = <46>;

- hsync-len = <1>;

- vback-porch = <22>;

- vfront-porch = <22>;

- vsync-len = <1>;

- hsync-active = <0>;

- vsync-active = <0>;

- de-active = <1>;

- pixelclk-active = <0>;

- };

- /*

- timing2: timing2 {

- mode_name = "TFT70AB";

- clock-frequency = <27000002>;

- hactive = <800>;

- vactive = <480>;

- hfront-porch = <23>;

- hback-porch = <46>;

- hsync-len = <1>;

- vback-porch = <22>;

- vfront-porch = <22>;

- vsync-len = <1>;

- hsync-active = <0>;

- vsync-active = <0>;

- de-active = <1>;

- pixelclk-active = <0>;

- };

- */

- };

- };

- };

- &pwm1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_pwm1>;

- status = "okay";

- };

- &pwm3 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_pwm3>;

- status = "okay";

- };

- &pwm7 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_pwm7>;

- status = "okay";

- };

- &pwm8 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_pwm8>;

- status = "okay";

- };

- &pxp {

- status = "okay";

- };

- /*

- &qspi {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_qspi>;

- status = "okay";

- ddrsmp=<0>;

- flash0: n25q256a@0 {

- #address-cells = <1>;

- #size-cells = <1>;

- compatible = "micron,n25q256a";

- spi-max-frequency = <29000000>;

- spi-nor,ddr-quad-read-dummy = <6>;

- reg = <0>;

- };

- };

- */

- &sai2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_sai2>;

- /*&pinctrl_sai2_hp_det_b>;*/

- assigned-clocks = <&clks IMX6UL_CLK_SAI2_SEL>,

- <&clks IMX6UL_CLK_SAI2>;

- assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

- assigned-clock-rates = <0>, <12288000>;

- status = "okay";

- };

- &uart1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_uart1>;

- status = "okay";

- };

- /*

- &uart2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_uart2>;

- /*fsl,uart-has-rtscts;

- /* for DTE mode, add below change

- /* fsl,dte-mode;

- /*pinctrl-0 = <&pinctrl_uart2dte>;

- status = "disable";

- };*/

- &uart2{

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_485>;

- fsl,rs485-gpio-txen = <&gpio1 31 GPIO_ACTIVE_HIGH>;

- linux,rs485-enabled-at-boot-time;

- status = "disable";

- };

- &uart3{

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_uart3>;

- status = "okay";

- };

- &usbotg1 {

- dr_mode = "otg";

- srp-disable;

- hnp-disable;

- adp-disable;

- status = "okay";

- };

- &usbotg2 {

- dr_mode = "host";

- disable-over-current;

- status = "okay";

- };

- &usbphy1 {

- tx-d-cal = <0x5>;

- };

- &usbphy2 {

- tx-d-cal = <0x5>;

- };

- &usdhc1 {

- pinctrl-names = "default", "state_100mhz", "state_200mhz";

- pinctrl-0 = <&pinctrl_usdhc1>;

- pinctrl-1 = <&pinctrl_usdhc1_100mhz>;

- pinctrl-2 = <&pinctrl_usdhc1_200mhz>;

- /* cd-gpios = <&gpio1 1 GPIO_ACTIVE_LOW>; */

- no-1-8-v;

- keep-power-in-suspend;

- enable-sdio-wakeup;

- vmmc-supply = <®_wifi_vmmc>;

- status = "okay";

- };

- &usdhc2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_usdhc2>;

- non-removable;

- status = "disable";

- };

- &gpmi {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_gpmi_nand>;

- status = "okay";

- nand-on-flash-bbt;

- };

- /*

- &wdog1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_wdog>;

- fsl,wdog_b;

- };

- */

- &spdif {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_spdif>;

- assigned-clocks = <&clks IMX6UL_CLK_SPDIF_SEL>,

- <&clks IMX6UL_CLK_SPDIF_PODF>;

- assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

- assigned-clock-rates = <0>, <49152000>;

- status = "okay";

- };

- &adc1 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_adc1>;

- vref-supply = <®_vref_3v3>;

- num-channels = <4>; //此参数为ADC的个数

- status = "okay";

- };

- &gpt2 {

- status = "okay";

- };

这是我的Makefile

- # KERNEL_DIR=/home/zzlyang/code/ebf_linux_kernel_6ull_depth1/build_image/build

- KERNEL_DIR=/home/zzlyang/code/ebf_6ull_linux

- ARCH=arm

- CROSS_COMPILE=arm-linux-gnueabihf-

- export ARCH CROSS_COMPILE

- obj-m := leddriver.o # 表示编译为Linux内核模块

- EXTRA_CFLAGS += -fno-pic -std=gnu99 -Wno-declaration-after-statement

- # EXTRA_CFLAGS :=-fno-pic -std=GNU99

- all:

- $(MAKE) -C $(KERNEL_DIR) M=$(CURDIR) modules

- EXTRA_CFLAGS="$(EXTRA_CFLAGS)"

- $(CROSS_COMPILE)gcc -o rgb_app rgbapp.c

- .PHONY:clean copy

- clean:

- $(MAKE) -C $(KERNEL_DIR) M=$(CURDIR) clean

- copy:

- sudo cp *.ko /home/embedfire/workdir

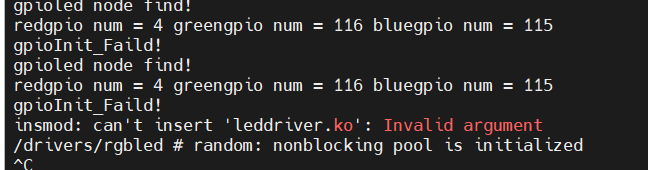

请问问题出在哪里?

- <div style="color: rgb(204, 204, 204); background-color: rgb(31, 31, 31); font-family: Consolas, "Courier New", monospace; line-height: 19px; white-space: pre;">

- </div>

|

|